|

|

汽车零部件采购、销售通信录 填写你的培训需求,我们帮你找 招募汽车专业培训老师

SATA(Serial ATA)硬盘,又称串口硬盘,是计算机机械硬盘的主流,已基本取代了传统的PATA硬盘。SATA的全称是Serial Advanced Technology Attachment,由Intel、APT、Dell、IBM、希捷、迈拓这几大厂商组成的Serial ATA委员会正式确立了Serial ATA 1.0规范,2002年,虽然串行ATA的相关设备还未正式上市,但Serial ATA委员会已抢先确立了Serial ATA 2.0规范。Serial ATA采用串行连接方式,串行ATA总线使用嵌入式时钟信号,具备了更强的纠错能力,与以往相比其最大的区别在于能对传输指令(不仅仅是数据)进行检查,如果发现错误会自动矫正,这在很大程度上提高了数据传输的可靠性。串行接口还具有结构简单、支持热插拔的优点。

SATA,即Serial ATA(串行 ATA),全称是Serial Advanced Technology Attachment,是由Intel、IBM、Maxtor 和 Seagate等公司共同提出的硬盘接口新规范。因为采用串行连接方式,所以使用 SATA 接口的硬盘又叫串口硬盘。SATA 规范将硬盘的外部传输速率理论值提高到了 150MB/s,比 Ultra ATA/100 高出 50%,比Ultra ATA/133 也要高出约 13%。SATAII 接口的速率可扩展到2X(300MB/s)和4X(600MB/s)。而 SATA150 与 SATAII 的区别主要是以传输数据的速度来划分的。未来的 SATA 将通过提升时钟频率来让硬盘也能超频,可彻底解决硬盘接口这一数据传输最终瓶颈。SATA 硬盘接口需要较新的主板南桥芯片来支持,如 Intel ICH6、Intel ICH7、nVIDIA nForce4、VIAVT8237和Si S964等。SATA的优势:支持热插拔 ,传输速度快,执行效率高。

每一个 SATA 硬盘存储结点由存储器控制接口 MCI 和 SATA 硬盘控制器构成,如图1所示。其中 MCI 负责按照消息帧格式生成、封装或解封装消息包,根据接收到消息包,提取并解析访问存储结点的操作命令,包括初始化,设置存储结点的节电模式、休眠或唤醒,读写存储器等。

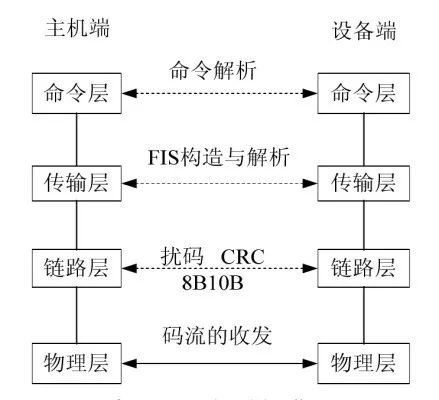

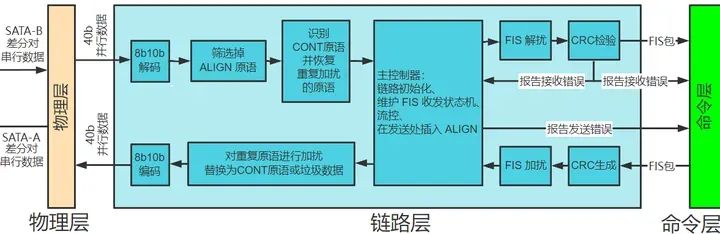

SATA 主机和 SATA 设备间的通信采用的是 SATA 协议, 按功能 SATA 协议分为物理层、链路层、传输层和命令层,协议的层次结构如图2所示。主机和设备之间,除了物理层通过SATA 接口实际物理连接,其他各层均通过消息虚拟连接。物理层是主机与设备之间的通信基础,主要负责码流的收发、将高速串行差分信号转换成并行数据以及将并行数据转换成高速串行差分信号;链路层主要负责消息的无差错传输,包括8B10B 编解码、加解扰、CRC校验等;传输层主要负责生成与解析帧信息结构(Frame Information Structures,FIS);命令层主要负责生成和解析访问 SATA 硬盘的操作命令。

物理层的下游用两对串行差分信号对连接 SATA device ,上游与链路层之间传输并行信号。物理层进行的主要工作包括:

时钟恢复:与常见的低速通信(例如几十MHz的老式硬盘的ATA并口)和中速通信(例如几百MHz的DDR3、MIPI LVDS)不同,在SATA这种几Gbps的高速率下,各个信号间难以进行对齐,因此SATA不是用用不同的信号线传输时钟,而通过8b10b编码把时钟和数据调制到同一对差分对上,因此物理层的 RX 通道需要使用锁相环 (PLL, 一种模拟电路) 对串行信号的时钟恢复,有了恢复出的时钟,才能对 RX 数据进行正确的采样。

串并转换:物理层的 RX 通道需要用恢复出的时钟把RX数据转换成以 10bit 为单位的并行信号;TX通道需要把链路层提供的 10bit 为单位的并行信号转换为串行信号发送出去。例如,对于 3Gbps 的 SATA Gen2 ,转换成的并行信号可以是 150MHz 20bit 位宽,也可以是 75MHz 40bit 位宽。

字节对齐:串并转换涉及到如何在串行的 bit 流中界定 10bit 并行单位的边界的问题,SATA 使用一种特殊的 ALIGN 原语来界定 byte 边界,在 8b10b 编码下,ALIGN 原语会产生一种独一无二的 10bit 组合模式,物理层负责识别这种模式,每当遇到这种模式,接收方就知道当前处于一个 10bit 的边界。

2.2 链路层、传输层概述

本文将链路层和传输层合起来讲,因为二者间耦合度较大,个人认为合起来更好理解。链路层和传输层需要实现:8b10b 编解码、原语生成和检测(包括FIS包边界识别)、加扰/解扰、CRC生成和检验、流控。最后,传输层与上游的命令层使用一种叫 Frame Information Structures (FIS) 的数据包结构进行交互。链路、传输层功能分别说明如下:

8b10b 编解码:物理层RX通道的并行数据是以 10bit 为单位的 8b10b 编码数据,链路层需要把它解码为 8bit (1byte) 的数据;而TX通道需要把 8bit 数据编码为 10bit 。显然 8b10b 编码会导致五分之一的带宽浪费,之所以设计这种冗余,是为了让 0 和 1 尽量均匀地分布,这样接收方才能对信号进行时钟恢复。

原语插入和检测:SATA 规定了几种原语 (Primitive) ,每个原语的长度都为 4byte 。原语并不携带数据,而是用来进行通信控制。本文涉及的原语包括 ALIGN, CONT, SYNC, R_RDY, R_IP, R_OK, R_ERR, X_RDY, SOF, EOF, WTRM, HOLD, HOLDA。原语有各自的功能,例如 ALIGN 原语用来进行字节对齐、X_RDY 原语用来告诉对方自己想发送一个 FIS 给对方,SOF 原语用来指示 FIS 的开头、EOF 原语用来指示 FIS 的结尾(通过 SOF 和 EOF 原语,RX通道才能正确地解析出 FIS 数据包的边界)。对于 TX 通道,需要正确地插入原语。对于 RX 通道,需要检测原语,并按原语规定的功能来进行状态机的状态转移。

FIS加扰/解扰:加扰器 (Scrambler) 和解扰器能生成一个伪随机数序列,每次复位后,生成的伪随机数序列是固定的。在 TX 通道,待发送的 FIS 数据需要与加扰器生成的伪随机数序列进行按位异或运算,称为加扰;在 RX 通道,收到的 FIS 数据需要与解扰器生成的伪随机序列也进行按位异或运算,称为解扰。因为两次异或后数据不变,确保了先加扰、后解扰后数据能够正确地被恢复。加扰的目的是让 SATA 电缆上传输的数据更加杂乱,从而让电磁辐射更加接近白噪声(而不是集中分布于某个频率),从而减少电磁干扰(EMI)。

原语的重复加扰:FIS 加扰只能减少FIS传输过程中的 EMI 。当SATA在传输大量重复原语时,为了减少EMI,需要使用另一种类似的机制:原语的重复加扰。该过程会用到 CONT 原语。

CRC生成和检验:TX 通道需要根据 FIS 数据计算出 CRC 并追加在 FIS 的最后;RX 通道需要根据收到的 FIS 数据生成 CRC ,并与收到的 CRC 进行对比(也即CRC检验)。若不匹配,说明 FIS 传输中出现误码,需要丢弃该 FIS 并向上游报告错误。

流控:硬盘介质的读写速率与 SATA 接口的速率往往并不匹配,因此传输层规定了流控(Flow Control)机制,流控依赖于 HOLD 和 HOLDA 原语,包括两种流控:

发送方流控:当发送方暂未准备好待发送的 FIS 数据时(例如读硬盘的速率慢于SATA接口速率),发送方可以插入 HOLD 原语来填空,这样就能支持“断断续续”地发送数据。

接收方流控:当接收方暂不能接收 FIS 数据时(例如写硬盘的速率慢于SATA接口速率),接收方可以向发送方发送 HOLD 原语,告诉发送方“不要发的这么快,我接受不了了”,发送方就会暂停发送数据并向接收方发送 HOLDA 原语来填空。

以上讲了这么多功能可能导致读者搞不清它们的逻辑关系,举例来说,一个链路层和传输层的结构图5。

图5:链路层和传输层的实现举例命令层概述

命令层:接受上游的读写命令,生成和解析命令FIS,实现硬盘读写操作。SATA 支持 ATA 和 ATAPI 命令集,每个命令集包含多种硬盘读写方式,比如 PIO 方式、 DMA 方式等,因此一个完整的命令层需要实现众多繁杂的命令的状态机,但其目的并不复杂,都是为了用各种方式来实现硬盘读写。本文仅会简单地介绍 DMA 方式:包括如何用 DMA 方式发送和接收 FIS ,从而进行硬盘的读写。

目前为止,读者已经对 SATA 协议栈有了粗浅的理解。下文将从链路层往上开始逐个讲解一些细节。本人并不了解物理层的细节,因此本文不讲物理层。

链路层、传输层详解

链路初始化

系统上电后,HBA 和 device 之间需要进行链路初始化(link initialize)。在初始化之前,HBA 和 device 之间显然还不能正常地传输 FIS 数据,因此 SATA 使用带外信号 (OOB signal) 来检测对方是否存在,从而进行链路初始化。之所以称为“带外”信号,是因为它是将差分对驱动到相同的公共电压,即不对应逻辑0也不对应逻辑1 。

规定差分线电平不同(逻辑0或逻辑1)为 SIGNAL ,差分线电平相同为 NOSIGNAL 。SATA 规定了两种 OOB 信号:

COMINIT :指持续发送 6 个 SIGNAL ,每个 SIGNAL 持续 106ns ,相邻两个 SIGNAL 间持续 320ns 的 NOSIGNAL 。

COMWAKE :持续发送 6 个 SIGNAL ,每个 SIGNAL 持续 106ns ,相邻两个 SIGNAL 间持续 106ns 的 NOSIGNAL 。

图6是链路初始化的时序图,首先,HBA 发送一个 COMINIT ,并等待 device 回复 COMINIT。如果没有收到 COMINIT,主机可以发送更多 COMINIT ,直到收到一个为止。然后主机向设备发送 COMWAKE,并等待 device 回复 COMWAKE 。此后,HBA 向 device 不断发送一个特殊的数据 DIAL-TONE (翻译为拨号音,是1和0交替的模式) ,并等待 device 发来 ALIGN 原语,device 发送 ALIGN 原语后, HBA 也发送 ALIGN 原语给 device ,即可完成链路初始化。初始化后,HBA 和 device 都向对方发送持续的 SYNC 原语,代表自己处于空闲状态,已经准备好收发 FIS 了。

传统的Parallel ATA使用单模信号放大系统“single-end-signal-amplified-system”。在这种系统中,噪声会随着正常信号一起传输、放大,不易被抑制;在高速时尤其严重,为了有效的减少噪声的干扰,我们只好使用高达5V的电压来传送正-常讯号,使大电压的正常讯号盖过小电压的噪声信号。虽然大的电压可以有效的抑制噪声,但是大的电压同时也表示驱动电路的生产成本将因此上升,大电压更不利于高速传输系统的设计和制造,高达5V的传输电压限制了追求高速和低成本的可能性。

和Parallel ATA相比,新的SATA使用了差动信号系统“differential-signal-amplified-system”。这种系统能有效的将噪声从正常讯号中滤除,良好的噪声滤除能力使得SATA只要使用低电压操作即可,和Parallel ATA 高达5V的传输电压相比,SATA只要0.5V(500mv) 的峰对峰值电压即可操作于更高的速度之上。“比较正确的说法是:峰对峰值‘差模电压’”。

和 Parallel ATA的5V驱动电压相比,0.5V的SATA系统节省电力,其驱动IC的生产成本也较为便宜。

|

|

|手机版|小黑屋|Archiver|汽车工程师之家

( 渝ICP备18012993号-1 )

|手机版|小黑屋|Archiver|汽车工程师之家

( 渝ICP备18012993号-1 )